Apm

Cand poate aparea o anti-dependenta?

O anti-dependență nu este posibil să apară

O anti-dependență poate apărea atunci când instrucțiunile nu sunt executate în ordine

O anti-dependență poate apărea atunci când mai multe instrucțiuni sunt executate în același moment de timp

O anti-dependență poate apărea atunci avem un hazard structural

O anti-dependență poate apărea doar în faza de IF

Modul de execuţie al unei întreruperi presupune:

Execuția unei întreruperi presupune obligatoriu existența unei benzi de asamblare

Redirecționa controlul fluxului de instrucțiuni într-o altă zonă

Redirecționarea controlului fluxului de instrucțiuni se va face pentru o perioadă limitată de timp

Execuția unei întreruperi presupune obligatoriu un procesor superscalar 10

La expirarea intervalului de timp necesar executării unei întreruperi se revine înapoi

Aparitia unei intreruperi precise presupune ca:

Toate instrucțiunile anterioare ei să fie kill la următorul ciclu de ceas şi toate instrucțiunile după ea să poată fi comise la următorul ciclu de ceas

Toate instrucțiunile anterioare ei să fie comise și toate instrucțiunile după ea să poată fi kill

Toate instrucțiunile anterioare ei să fie comise la următorul ciclu de ceas și toate instrucțiunile după ea să poată fi kill

Toate instrucțiunile anterioare ei să fie kill și toate instructiunile după ea să poată fi comise la urmatorul ciclu de ceas

Toate instrucțiunile anterioare şi după vor fi kill

Când procesorul decide să proceseze o întrerupere execută: 1. Opreşte programul curent la instrucțiunea I(i), terminând complet execuția tuturor instrucțiunilor până la I(i- 1)-întrerupere precisă. 2. Salvează PC-ul instrucţiunii I(i) într-un registru special EPC ۵ 3. Dezactivează întreruperile şi transferă controlul către o întrerupere desemnată de controller-ul de întreruper care rulează în kernel mode Ce se întâmplă în cazul în care apare o nouă întrerupere în timpul tratării unei întreruperi?

O soluție ar fi să ștergem EPC-ul şi apoi reluăm întreruperile în interiorul întreruperii

O soluție ar fi să memorăm PC+4 şi apoi reluăm întreruperile în interiorul întreruperii

O soluție ar fi să memorăm EPC-ul în memorie și apoi reluăm întreruperile în interiorul întreruperii

O soluţie ar fi să ignorăm complet această posibilitate

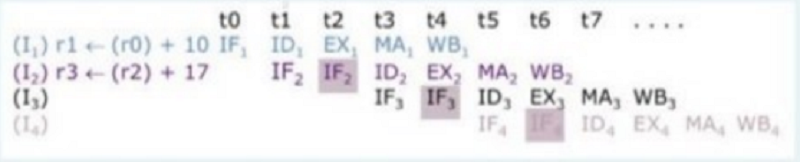

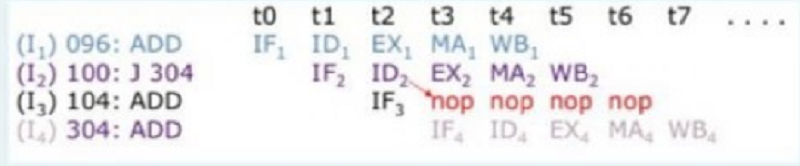

Se consideră următoarea execuție a unui program în bandă de asamblare. Așa cum se poate observa în execuția programului au fost introduse nişte NOP-uri. De ce?

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi JUMP atunci am avea hazard de control

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi BRANCH atunci am avea hazard de date

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi BRANCH atunci am avea hazard de control

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi JUMP atunci am avea hazard structural

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi JUMP atunci am avea hazard de date

Fără aceste NOP-uri în cazul în care prima instrucțiune ar fi BRANCH atunci am avea hazard structural

Clusterelor superscalare presupun legarea în paralel a mai multor procesoare superscalare. Modalitatea de funcţionare a acestor clustere presupune:

Nu există o astfel de posibilitate pentru procesoarele superscalare

Putem face switch între pipe_1 și pipe 2 iar în interiorul fiecărui pipe mai avem 2 pipe-uri între care putem face de asemenea switch

Nu putem face switch între pipe_1 şi pipe 2 iar în interiorul fiecărui pipe mai avem 2 pipe-uri între care putem face de asemenea switch

qutem face switch între pipe_1 şi pipe 2 iar în interiorul fiecărui pipe mai avem 2 pipe-uri între care nu mai putem face switch

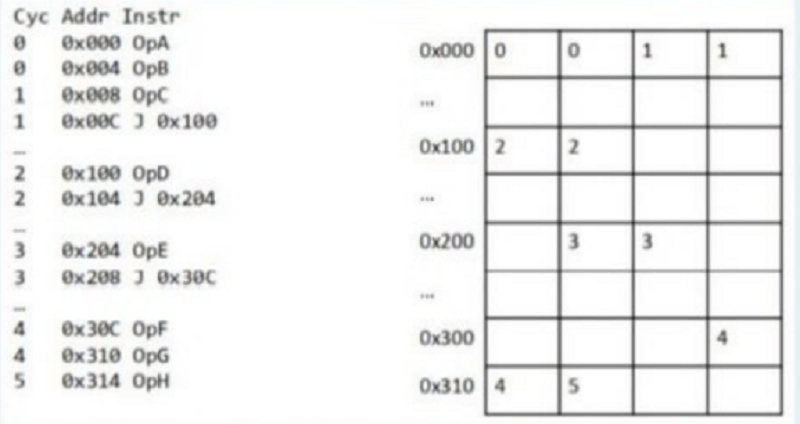

Se presupune execuția următorului program şi maparea instrucțiunilor in memoria cache de instrucțiuni conform figurii de mai jos. Totodată se presupune că nu avem JUMP. Aşa cum se poate observa in figură, memoria poate conţine 4 instrucțiuni pe o linie iar într-un ciclu de ceas se citesc 2 instrucțiuni odată (inclusiv pentru ciclul 4). Ce tip de memorie cache de instrucțiuni este necesară pentru a fi fezabil acest tip de citire?

O memorie cache de instrucțiuni single port cu o capacitate putere a lui

O memorie cache de instrucțiuni single port

O memorie cache de instrucțiuni dual port

O memorie cache de instrucțiuni cu cel puțin 4 porturi

O memorie cache de instrucțiuni cu cel mult 4 porturi

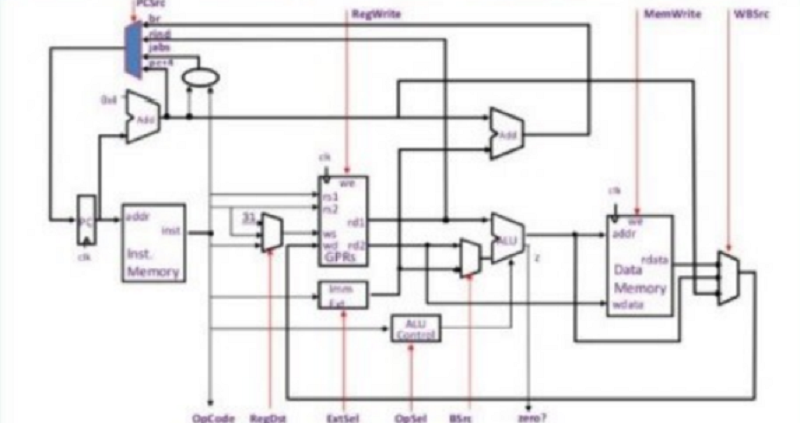

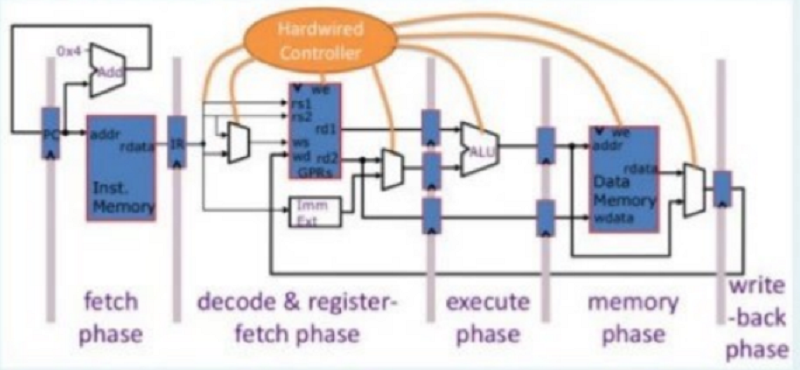

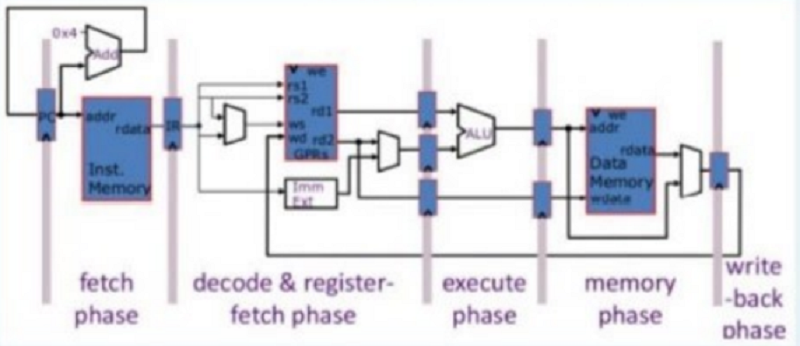

Execuția unei instrucțiuni în cazul procesorului de mai jos fără bandă de asamblare:

Presupune necesitatea unui ciclu de ceas mic

Presupune necesitatea unui ciclu de ceas mare

Figura nu prezintă semnale de control, deci nu se poate numi un procesor, ca atare nu poate executa instrucțiuni

Presupune trecerea prin toate elementele de la stânga la dreapta

Presupune trecerea prin toate elementele dar nu contează ordinea

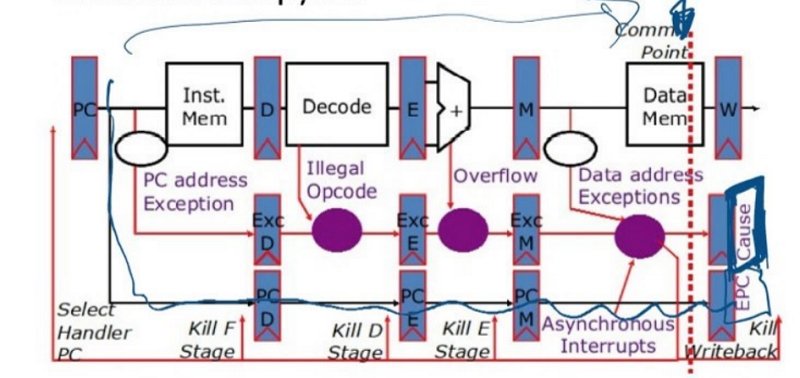

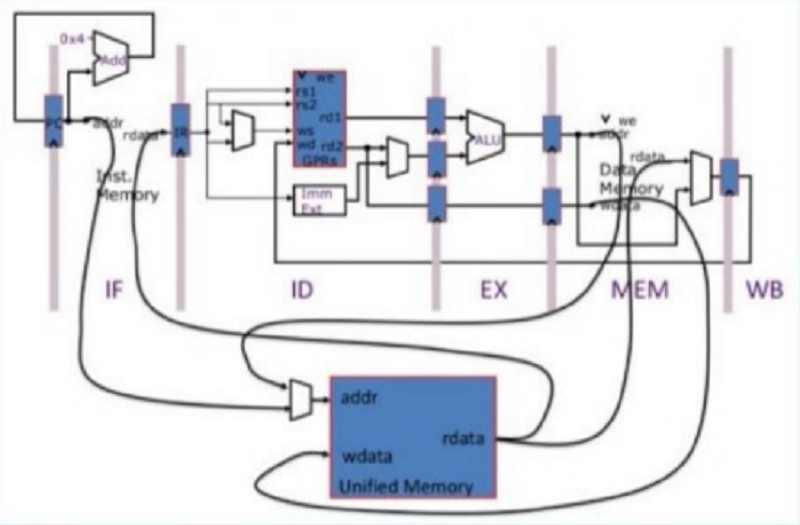

În cadrul figurii de mai jos, CP-ul este pus la finalul benzii de asamblare. De ce nu este el pus la finalul stagiului EX ?

El se pune obligatoriu la finalul benzii de asamblare intodeauna

Putem stabili dacă folosim sau nu CP exact ca în cazul procesoarelor 000

El trebuie pus cât mai devreme în banda de asamblare deoarece este bine ca excepțiile să stea cât mai puțin în banda de asamblare

Ar fi mai bine să fie pus în faza de EX sau chiar în faza de ID

El trebuie pus acolo unde nu mai pot fi luate excepții în pipe

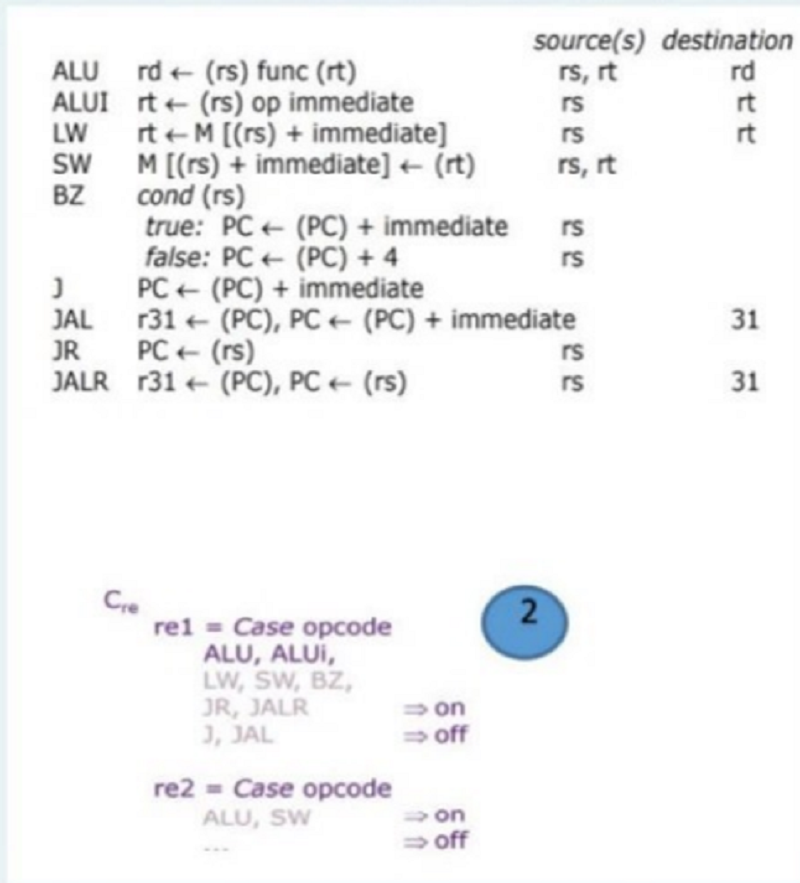

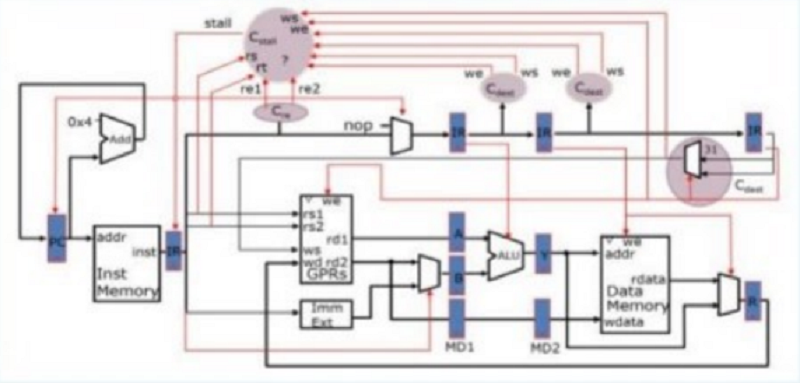

In cadrul determinării semnalului de control C_STALL etapa a doua presupune introducerea a două ecuații: re1 şi re2. De ce?

Cele 2 ecuații reprezintă valorile realocate din cadrul unor registre folosite doar de instrucțiunile JALR şi JAL

Cele 2 ecuații reprezintă valorile realocate din cadrul unor registre folosite de anumite instrucțiuni

Instructiunile JALR şi JAL scriu întotdeauna şi apoi nimic nu mai scrie fişierul de registre, ca atare ret este folosit pentru citirea primului operand cât timp re2 este folosit pentru citirea celui de al doilea operand

Avem nevoie obligatoriu doar de re1. re2 poate că se referă la operandul 2 dar cum se poate vedea și în figură el va trebui să acopere instrucțiunea SW care nu are un al doilea operand. Ar trebui eliminat pentru creşterea performanței benzii de asamblare

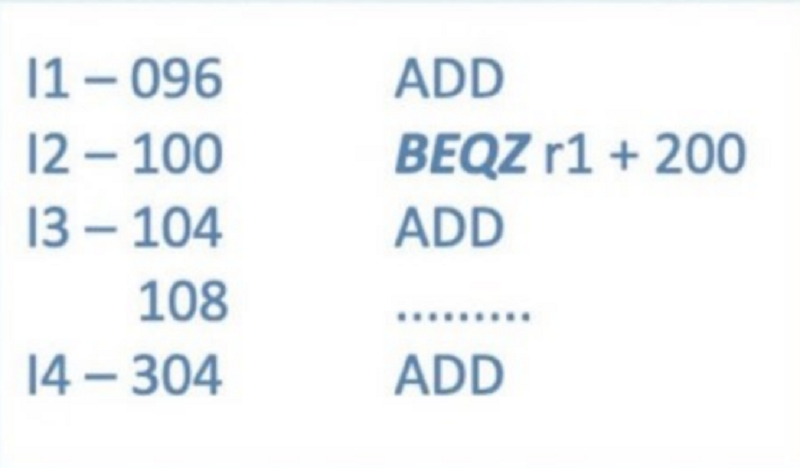

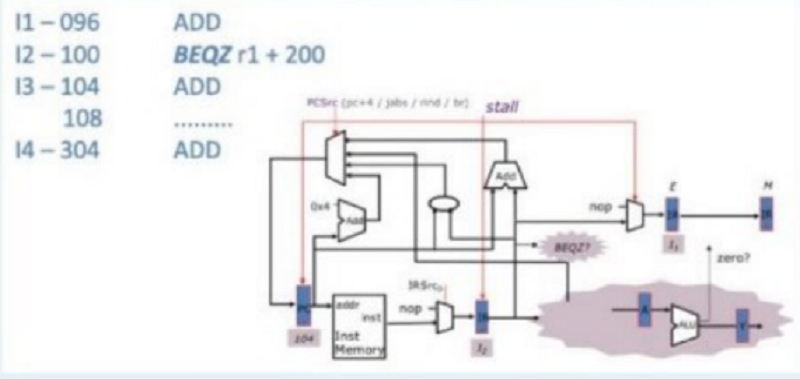

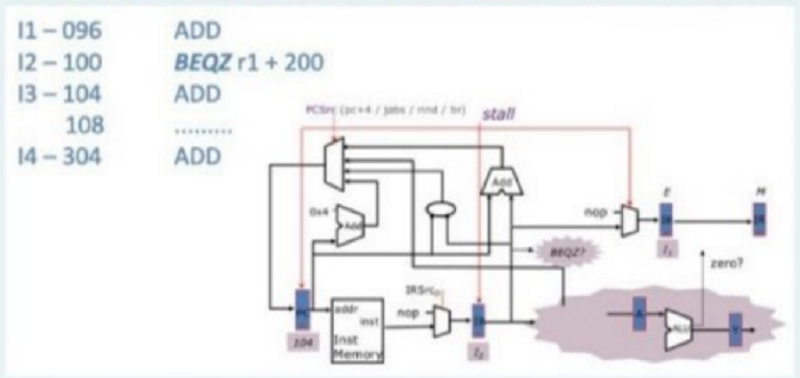

Se consideră programul de mai jos executat în bandă de asamblare. Când se poate face eliminarea instrucțiunilor 104 şi 108 ?

După faza de MEM

După faza de IF

După faza de WB

După faza de ID

După faza de EX

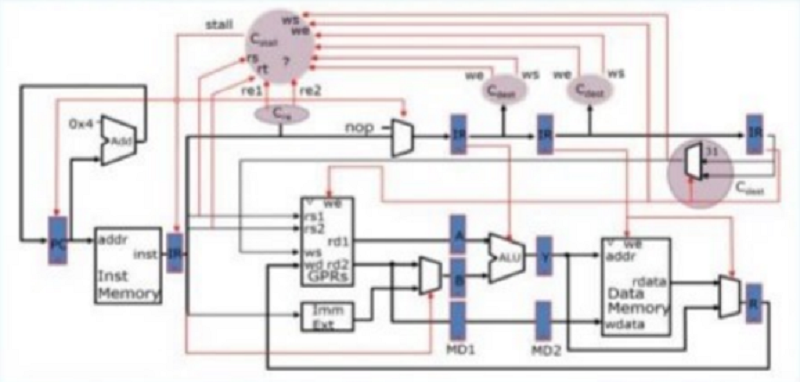

Se consideră implementarea unui procesor ca in figura de mai jos. De ce este MUX-ul din stagiul WB incercuit ?

Avem nevoie de IR deoarece salturile şi legăturile doar citesc și din acest motiv este nevoie de IR

Destinația nu este codată în câmpul RD al instrucțiunii aşa că IR este hardcodat cu 31

Deoarece poate fi văzut ca un registru JAL către o destinaţie implicită

Avem nevoie de IR deoarece salturile și legăturile doar scriu și din acest motiv este nevoie de IR

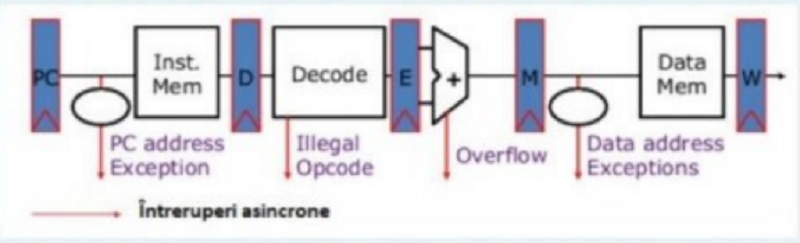

Conform figurii de mai jos care este cea mai veche întrerupere din banda de asamblare ?

Nici una deoarece nu există un sistem de prioritizare ca să ne dăm seama

Overflow

Illegal opcode

Data address exception

PC address exception

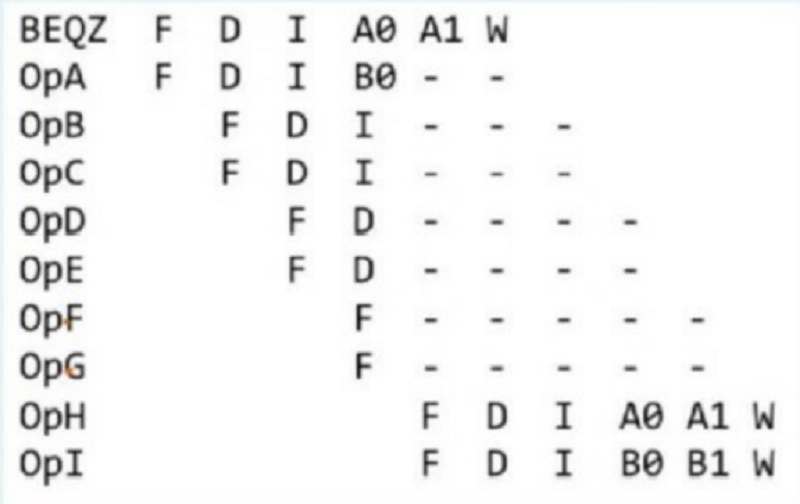

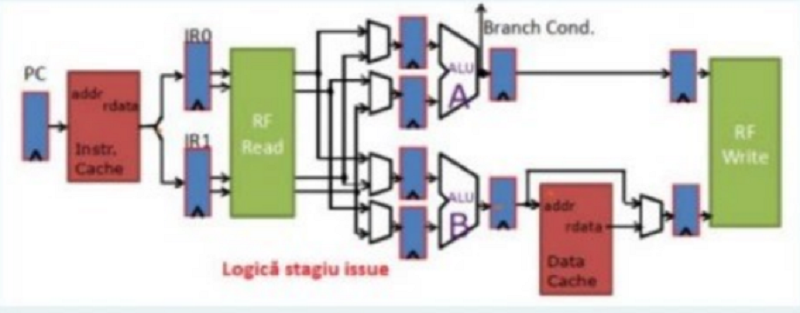

Se consideră execuția unui program conform figurii de mai jos. După cum se poate observa din execuția programului, instrucțiunea BEQZ este luată abia în etapa A0 ceea ce implică ca următoarele 7 instrucțiuni să fie KILL. Acest lucru conduce la un impact foarte mare asupra CPI-ului. Ce soluții avem de îmbunătăţire?

Nu avem nici o soluție viabilă pentru acest tip de procesor

Mărirea numărului de stagii de pipe care preced stagiul A0 pentru obţinerea unei predicţii cât mai bune

Mărirea numărului de stagii de pipe care preced stagiul AO

Implementarea unui predictor de branch-uri cât mai bun

Micsorarea numărului de stagii de pipe care preced stagiul AO

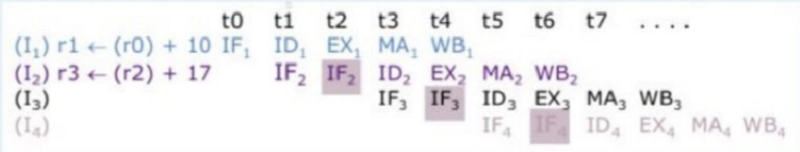

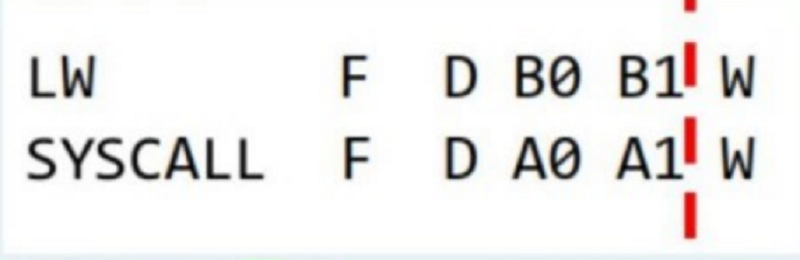

Se consideră execuția a două instrucțiuni ca în figura de mai jos. În cazul în care instrucțiunile sunt executate altfel decât sunt prezentate in figura de mai jos ce trebuie făcut?

Eliminăm instrucţiunea LW

Ignorarea instrucțiunii SYSCALL

Ignorarea rezultatului instrucțiunii LW

Nu trebuie făcut nimic

Eliminăm instrucțiunea SYSCALL

Modul de execuție al unei întreruperi presupune:

Execuția unei întreruperi presupune obligatoriu existenţa unei benzi de asamblare

Redirecţionarea controlului fluxului de instrucțiuni se va face pentru o perioadă limitată de timp

Redirectiona controlul fluxului de instrucțiuni într-o altă zonă

La expirarea intervalului de timp necesar executării unei intreruperi se revine inapoi

Execuția unei întreruperi presupune obligatoriu un procesor superscalar IO

Pentru execuția următorului program in bandă de asamblare se presupune că instrucţiunea 3 are nevoie de STALL și în acelaşi moment de timp trebuie să facem KILL. Este important ca instrucțiunea din stagiul DECODE să fie invalidă ?

Subiect netratat la curs

Nu, deoarece STALL-ul trebuie să aibă prioritate minimă

Da, deoarece STALL-ul trebuie să aibă prioritate maximă

Nu

Nu are nici o importanță invaliditatea instrucţiunii din stagiul de DECODE

Da

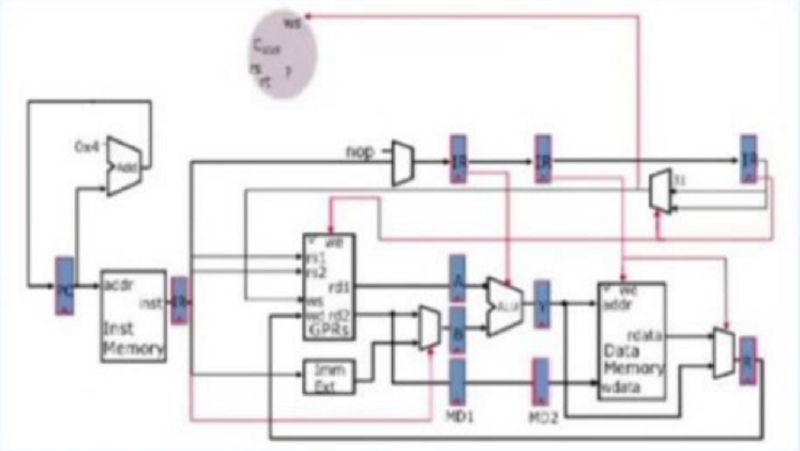

Se consideră implementarea procesorului de mai jos. În execuția unui program trebuie introdus STALL atunci când:

RT al instrucțiunii aflate în stagiul EX nu este egal cu OPCODE al unei instrucțiuni necomise

RT al instrucţiunii aflate în stagiul IF nu este egal cu OPCODE al unei instrucțiuni necomise

RS al instrucțiunii aflate în stagiul ID nu este egal cu RD al unei instrucţiuni necomise

RT al instrucţiunii aflate în stagiul EX egal cu OPCODE al unei instrucţiuni necomise

Immediate 16 al instrucțiunii aflate în stagiul IF nu este egal cu immediate26 al unei instrucțiuni necomise

RT al instrucţiunii aflate in stagiul IF egal cu OPCODE al unei instrucțiuni necomise

RS al instrucțiunii aflate in stagiul ID egal cu RD al unei instrucțiuni necomise

Immediate 16 al instrucțiunii aflate în stagiul IF egal cu immediate26 al unei instrucțiuni necomise

Se consideră implementarea unui procesor ca în figura de mai jos. Când nu trebuie trebuie verificată condiția de STALL şi de ce?

Condiția de STALL nu trebuie verificată în cazul instrucțiunilor in care operandul 2 este inclus in instrucțiune

Condiția STALL nu trebuie verificată in cazul instrucțiunilor care nu citesc un registru

În cazul instrucțiunii SW deoarece nu scrie nici un registru

Condiția de STALL trebuie verificată întotdeauna

În cazul instrucțiunii LW deoarece se scrie un registru

Misiunea unui arhitect de calculatoare este aceea de a lua decizii cât mai subtile de proiectare pentru a îndeplini anumite cerințe precum:

Consum de putere cât mai mare pentru a face calculatorul să ruleze cât mai rapid

O durată de viață cât mai mare a arhitecturi

Consum de putere cât mai mic pentru a face calculatorul să ruleze cât mai rapid

Uşurinţă în programare

O durată de viață cât mai mică a arhitecturi pentru a permite conceptelor noi să fie imediat exploatate

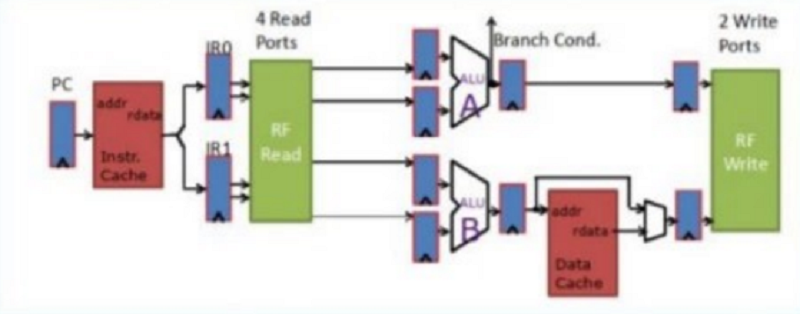

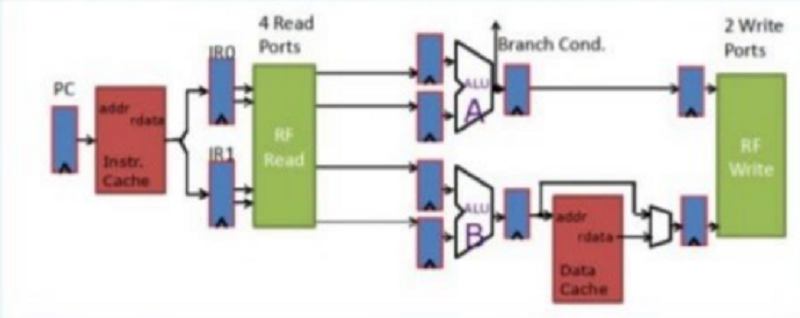

În cazul unui procesor superscalar 10 cu 2 cái ca în figura de mai jos sunt planificate spre execuție 2 instrucţiuni. O instrucțiune LW in registrul IR0 şi o instrucţiune ADD în registrul IR1. Se pot ele executa?

Nu deoarece registrul IRO are 4 ieşiri iar operația LW are un singur operand

Da, deoarece procesorul este prevăzut cu 2 căi de execuţie

Nu

Da

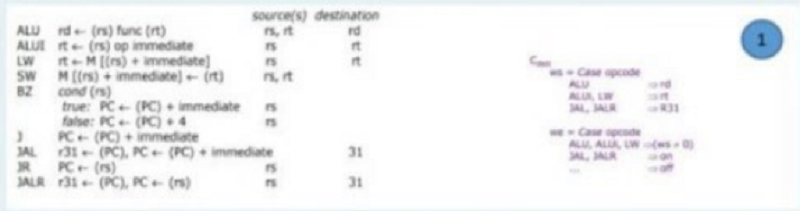

Primul pas in determinarea semnalului C_STALL este determinarea semnalului C_DEST aşa cum se prezintă în figura de mai jos. De ce este nevoie de ws şi de we? Dar de CASE?

CASE este folosit pentru a identifica tipul instrucţiunii. ws şi we sunt necesare deoarece câte o dată se scrie o destinaţie

CASE este folosit pentru a identifica tipul instrucțiunii. Ws este în plus, se poate și fără el. We este semnalul care ne spune dacă este nevoie să scriem sa nu.

CASE este folosit pentru a identifica tipul instrucţiunii. ws și we sunt necesare deoarece câte o dată se scrie o destinație sau nu

CASE este folosit pentru a identifica tipul instrucţiunii. ws și we sunt necesare deoarece câte o dată se citește o destinaţie sau nu

CASE este folosit pentru a identifica tipul instrucţiunii. ws şi we sunt necesare deoarece câte o dată se citeşte o destinaţie

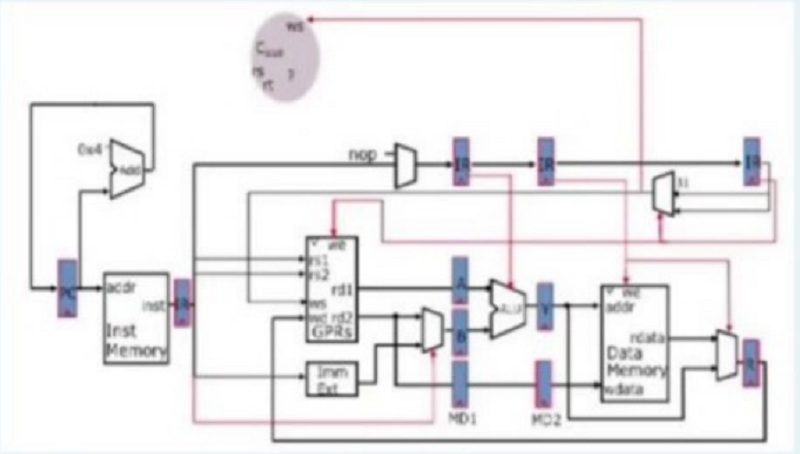

În cazul căii de date a unui procesor MIPS cu bandă de asamblare una din posibilitățile de implementare ale controlului se prezintă în figura de mai jos. Această implementare conduce la următoarele concluzii:

Nu este o implementare bună deoarece unitatea de control nu este proiectată într-o manieră de tip bandă de asamblare

Nu este necesară introducerea de registre pentru a fi capabili să executăm o instrucțiune în mai mulți ciclii de ceas

instrucţiunile nu pot fi executate in bandă de asamblare

Fără anumite modificări CPI-ul va creşte - va trebui să adăugăm resurse hardware

Este necesară introducerea de registre pentru a fi capabili să executăm o instrucțiune în mai mulți ciclii de ceas

Se consideră calea de date MIPS prevăzută cu bandă de asamblare. Pentru fiecare stagiu al benzii de asamblare se consideră câte un timp de execuţie astfel: tIM, RF, LALU, DM, tRW. Frecvenţa ceasului care va controla banda de asamblare cel mai probabil va fi oferită de:

T_RW

T_ALU

T_DM

T_IM

T_RF

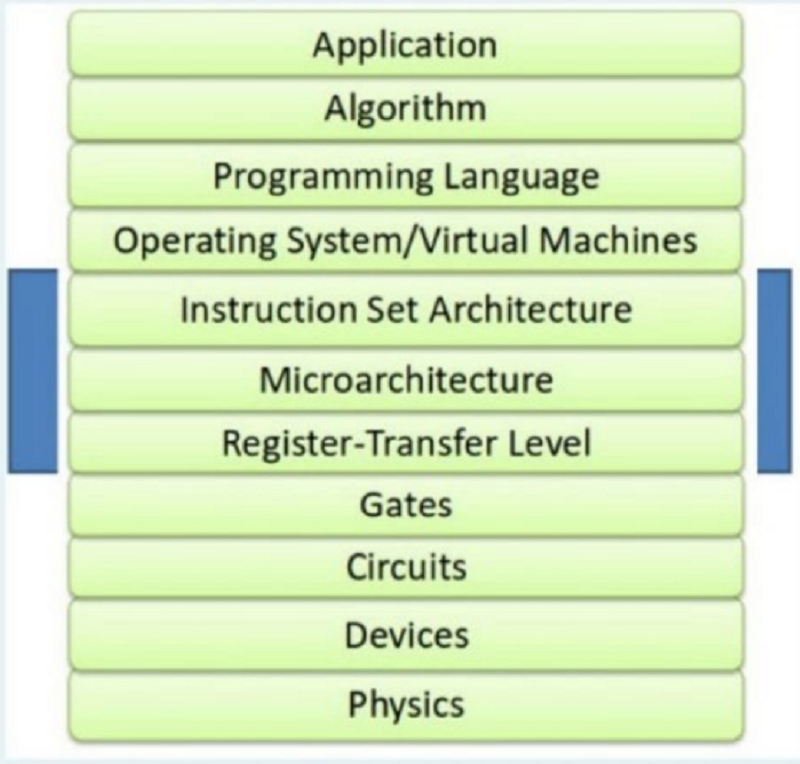

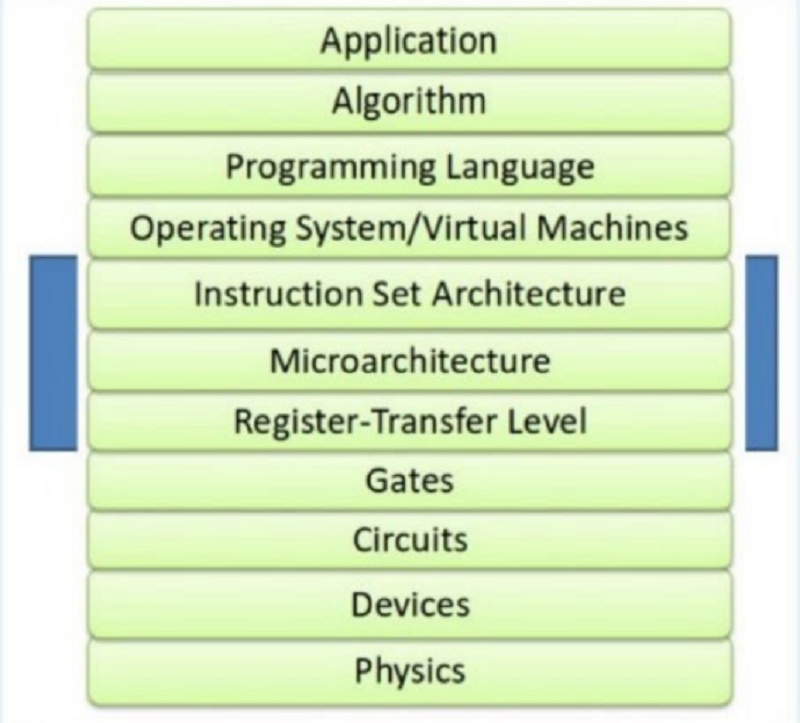

Conform figurii de mai jos există un layer denumit "Register-Transfer Level". Acest nivel permite descrierea unui circuit/dispozitiv electronic prin:

Intermediul limbajului VHDL

Prin intermediul limbajului C++

Intermediul limbajului Verilog

Prin intermediul limbajului Python

La inceput fiecare procesor avea (până în 1960):

Propriul său set de instrucțiuni

Un sistem de memorie cache organizat pe nivele pentru obţinerea unei performanțe mărite

Un sistem de memorie cache organizat pe minim două nivele pentru obţinerea unei performanțe mărite

Propriul său sistem de I/O și storage secundar

Propriile sale asambloare, compilatoare și librării

În cazul in care dorim să facem bypass intre clustere superscalare vom avea nevoie de:

3 extra cicluri de ceas

2 extra cicluri de creas

Nu putem face această operație deoarece se va genera un hazard structural

4 extra cicluri de ceas

Un extra ciclu de ceas

este important să avem compilatoare cât mai inteligente deoarece:

Eliminăm mai uşor instrucțiunile care nu sunt definite în ISA

Eliminăm mai uşor instrucțiunile care sunt interdependente

Astfel eliminăm mai uşor instrucțiunile redundante

Eliminăm mai uşor instrucțiunile care nu ne sunt utile

Eliminăm mai uşor instrucțiunile mai lungi

Se consideră straturile de abstractizare din figura de mai jos. Microarhitectura se referă la:

Modalitatea de construire a unui chip cât mai general care să acopere toate necesitățile unui utilizator

Organizarea sistemelor de calcul strict orientată pe consumul de putere

Noţiunea nu a fost prezentată la curs

Organizarea sistemelor de calcul

Modalitatea de construire a unui chip specific

O intrerupere sau o exceptie este denumita precisa prin definitie daca:

Apare doar în cadrul unui procesor OOO

Terminarea execuției unei instrucţiuni se face înainte de a începe execuția următoarei instrucțiuni

Execuția unei instrucțiuni se face în paralel cu execuția următoarei instrucţiuni

Starea procesorului salvat corespunde modelului secvenţial de execuție a programului

Apariția unei intreruperi imprecise nu este posibilă

Se consideră un procesor implementat conform figurii de mai jos şi execuția următoarelor instrucțiuni LW, ADD, ADD, ADD. În execuția programului trebuie introdus un stall? Daca da, unde ?

Trebuie introdus stall

Dacă avem stall atunci stall trebuie făcut pe a doua instrucțiune ADD

Dacă avem stall atunci stall trebuie făcut pe prima instrucțiune ADD

Dacă avem stall atunci stall trebuie făcut pe ultima instrucțiune ADD

Nu contează introducerea de stall deoarece este un hazard structural si el nu poate fi evitat f. Nu trebuie introdus stall

În cadrul unui procesorului de mai jos, a fost stabilit la curs că putem introduce logică pentru bypass în 6 puncte conform figurii de mai jos. Logica selectării acestor puncte creşte odată cu mărirea dimensiunilor benzilor de asamblare. Cum eliminăm acest inconvenient?

Avem in vedere o execuție a instrucțiunilor într-o maniera OOO

Nu aplicăm full bypass

Eliminarea unor anumite resurse hardware

Implementăm clustere superscalare

Facem bypass doar la anumite locații

ISA este un layer abstract

Menit a se schimba / modifica nu foarte des

Menit a se schimba / modifica foarte des

Noțiune neprezentată la curs

Oferit software-ului

Oferit hardware-ului

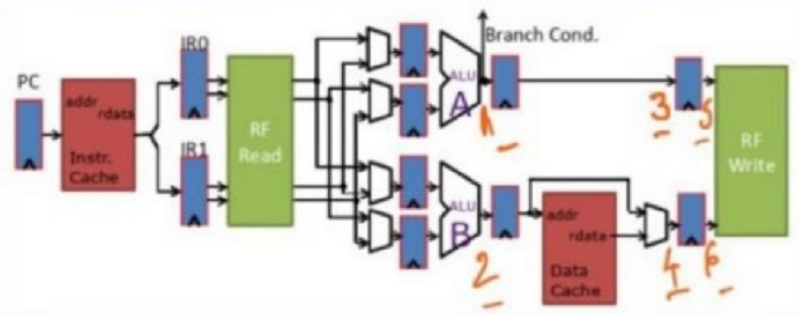

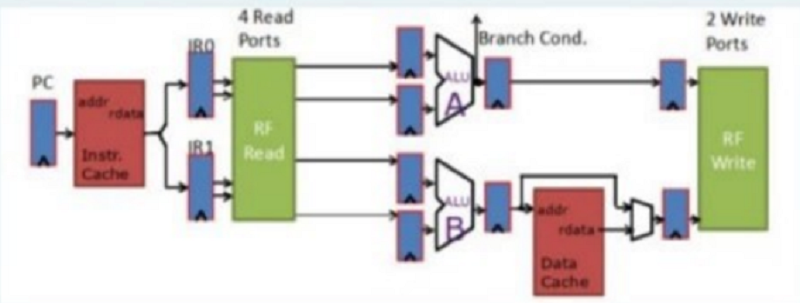

În cazul unui superscalar 10 pe 2 cái registrul RF are nevoie de 4 porturi de intrare, aşa cum se poate observa in figura de mai jos. De ce?

Deoarece într-un astfel de procesor citirea se poate selectiv

Deoarece conținutul registrelor IR nu pot fi simultan oferite la ieșire ci doar la ciclii de ceas consecutivi

Deoarece un astfel de procesor poate executa doar operații cu întregi şi salturi

Deoarece registrul de scriere RF are 2 porturi iar 4 este putere a lui 2

Deoarece numărul de instrucțiuni ce poate fi executat este dublu

În cazul unei benzi de asamblare ideale:

Putem partaja resurse fără restricții între stagii

Ordinea stagiilor poate fi modificată

Putem partaja resurse cu restricții intre stagii

Nu putem partaja resurse intre stagii

Ordinea stagiilor nu poate fi modificată

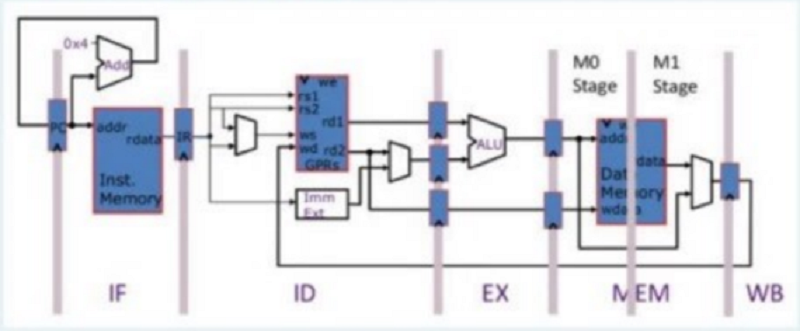

Se consideră următorul procesor şi execuția următorului program: ADD, LW, LW, ADD. Există hazard structural pe primele 2 instrucțiuni la MO şi M1? Dar pe ultimele două instrucțiuni la MO şi M1?

Nu există hazard structural pe ultimele 2 instrucțiuni la MO şi M1

Există hazard structural pe ultimele 2 instrucțiuni la MO şi M1

Ar fi hazard structural dacă instrucțiunile ar fi identice

Există hazard structural pe primele 2 instrucțiuni la MO și M1

Nu există hazard structural pe primele 2 instrucțiuni la MO şi M1

În cazul unui procesor superscalar 10 cu 2 căi ce conţine faza de FETCH?

În faza de FETCH vom avea PC şi PC+4

In faza de FETCH vom avea decodificarea instructii

In faza de FETCH vom avea determinarea instructii

In faza de FETCH vom avea două instrucțiuni simultan

In faza de FETCH vom avea eliminarea instrucțiunilor JAL și JALR

O dependenta iesire cand poate aparea?

O dependență de ieșire poate apărea doar în faza de IF

O dependență de ieşire poate apărea doar în faza de ID

O dependență de ieşire nu este considerată un hazard

O dependență de ieşire poate apărea în cazul execuției a 5 sau mai multe operații

O dependență de ieșire poate apărea în cazul execuției a 2 operații care necesită toți ciclii de ceas

Se consideră următoarea execuție a unui program în bandă de asamblare. De ce este nevoie de introducerea NOP-urilor în execuția programului cu toate că programul nu prezintă hazard-uri?

Se evită hazardul de control deoarece trebuie determinată instrucțiunea 2

Programul nu prezintă hazarduri şi ca atare nu trebuiesc puse NOP-uri

Se evită hazardul de date deoarece trebuie determinată instrucțiunea 2

Nu trebuie puse NOP-uri

Se evită hazardul structural deoarece trebuie determinată instrucţiunea 2

Execuția următorului program in bandă de asamblare presupune eliminarea instrucțiunilor 104 şi 108. Pentru aceasta este nevoie:

Introducerea unui MUX suplimentar

Introducerea de noi registre

Introducerea de NOP-uri

Introducerea unei memorii de instrucţiuni

Schimbată condiţia pentru IRSrc

Introducerea unei memorii de date

În cazul unui procesor superscalar 10 cu 2 cái ca în figura de mai jos sunt planificate spre execuție 2 instrucțiuni. O instrucțiune LW in registrul IRO şi o instrucțiune ADD in registrul IR1. Ce mai trebuie adăugat ca să poată fi posibilă execuția celor 2 instrucţiuni ?

O logică suplimentară care să permită duplicarea operandului/operanzilor uneia sau mai multor instrucțiuni

Folosirea a două decodificatoare

O logică suplimentară care să permită switch între instrucţiuni

Duplicarea logicii de control

Se consideră următoarea implementare a unui procesor pentru determinarea semnalului C_STALL. Ce trebuie verificat în acest caz ?

Practic se verifică câmpul RS din cadrul unei instrucțiuni MIPS

Se verifică valoarea registrului

Practic se verifică câmpul RD din cadrul unei instrucțiuni MIPS

Practic se verifică câmpul immediate 16 din cadrul unei instrucțiuni MIPS

Practic se verifică câmpul OPCODE din cadrul unei instrucțiuni MIPS

Practic se verifică câmpul immediate26 din cadrul unei instrucțiuni MIPS

Practic se verifică câmpul RT din cadrul unei instrucțiuni MIPS

Se consideră execuția programului de mai jos in bandă de asamblare. Se presupune că speculăm valoarea PC+4. Instrucțiunea 2 nu face STALL deoarece avem speculație dar de ce instrucțiunea 3 introduce doar fetch?

Conform enunțului există speculație PC +4, ca atare, după instrucțiunea 2 trebuie să înceapă instrucțiunea 3. Speculația fiind greșită, instrucțiunea 3 trebuie eliminată din banda de asamblare.

Conform enunțului există speculație PC+4, ca atare, după instrucțiunea 2 trebuie să înceapă instrucțiunea 3. Cu toate acestea, execuția instrucţiunii 3 ar conduce la un hazard structural, ca atare va trebui eliminată din banda de asamblare

Conform enuntului există speculație PC+4, ca atare, după instrucţiunea 2 trebuie să înceapă instrucţiunea 3. Cu toate acestea, execuția instrucţiunii 3 ar conduce la un hazard de control, ca atare va trebui eliminată din banda de asamblare

Programul nu poate fi executat în bandă de asamblare deoarece prezintă instrucţiuni ce nu pot fi executate in bandă de asamblare

Conform enunțului există speculație PC+4, ca atare, după instrucțiunea 2 trebuie să înceapă instrucțiunea 3. Cu toate acestea, execuția instrucțiunii 3 ar conduce la un hazard de date, ca atare va trebui eliminată din banda de asamblare

{"name":"Apm", "url":"https://www.quiz-maker.com/QPREVIEW","txt":"Cand poate aparea o anti-dependenta?, Modul de execuţie al unei întreruperi presupune:, Aparitia unei intreruperi precise presupune ca:","img":"https://www.quiz-maker.com/3012/CDN/98-4822820/screenshot-2024-02-08-153318.png?sz=1200"}

More Quizzes

AVID BLOCK 1 REVIEW

20100

CYBER BULLYING

630

DES 2016

100

100

Soil Fertility and Fertilizers

15831850

Free Financial Decision-Making

201028099

Free Equine Lameness: Test Your Diagnostic Skills

201027251

Free Substance Use Awareness

201021726

Which Sector V KND Character Are You? Free Personality

201023997

Ultimate Yammy Xox Trivia: Test Your Gamer IQ

201042318

Does My Dog Really Love Me? Take the to Find Out

201023997

Think You Know Bigg Boss 11? Take the Ultimate!

201050771